# L3M Device Level 3 Mapper TXC-03452

DATA SHEET Product Preview

# DESCRIPTION

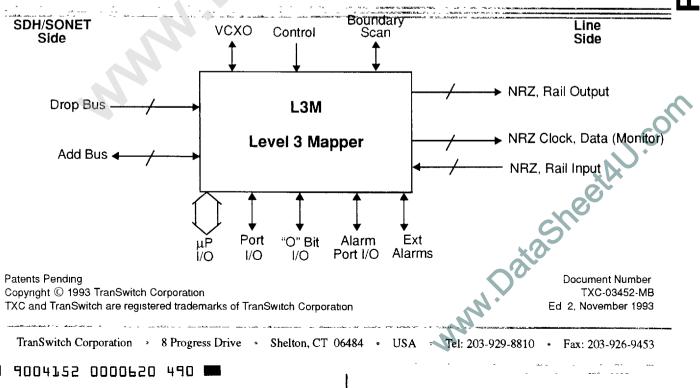

The L3M maps a DS3 or E3 line signal into an STM-1/ STS-3/STS-1 formatted signal. The L3M provides a TUG-3 formatted signal for STM-1 operation, or an STS SPE for STS-3 or STS-1 operation. The SDH/SONET signal is transmitted via an add bus with timing derived from the drop side, add side or from external timing (STS-1 only). An option is provided to generate the A1, A2 framing pattern, C1 byte and H1, H2 pointer towards the add bus when external timing mode is selected.

Individual POH bytes for the transmitted SDH/SONET signal are mapped from the L3M memory map or an external interface. An option is provided to generate an unequipped status or TUG-3 path AIS signal. External accesses are provided for the communications channel "O"-bit and alarms for ring operation. The received signal is desynchronized from drop bus STM-1/TUG-3, STS-3/STS SPE, or STS-1 signal. Internal pointer processing is performed for the TUG-3 signal. All POH bytes are provided for the microprocessor.

# Add/drop multiplexers

- Digital cross-connect systems

- Broadband switching systems

- Transmission equipment

Maps the following line formats into SDH/SONET format:

-DS3 to/from STS-3/STS-1 SPE or STS-1 SPE -E3 to/from STM-1/TUG-3

SDH/SONET bus access:

FEATURES

Drop/add data byte access (with clock, C1J1, SPE, and parity)

-Add bus interface timing derived from drop bus, add bus, or external timing

- Path overhead byte processing:

Processor or external interface

B3 generation and detection with test mask

B3 performance counter (16 bit) and block error counter (8 bit)

- -C2 mismatch and unequipped detection -G1 processing

- Microprocessor access:

-Motorola or Intel compatible (pin selectable)

-Hardware/software interrupt capability

- · Line Interface

- -Transmit and receive NRZ or rail operation with split operation capability

- Testing functions:

- -SONET, facility, or line loopback

- -Transmit and receive 2<sup>15</sup>-1 or 2<sup>23</sup>-1 generator & analyzer

- -Boundary scan capability

Tran-Ð MÍGĽ

\_\_\_\_\_

\_ \_

# TABLE OF CONTENTS

| SECTION                              | PAGE  |

|--------------------------------------|-------|

|                                      |       |

| Block Diagram                        | 3     |

| Block Diagram Description            | 3-6   |

| Pin Diagram                          | 7     |

| Pin Descriptions                     | 8-17  |

| Absolute Maximum Ratings             | 18    |

| Thermal Characteristics              | 18    |

| Power Requirements                   | 18    |

| Input, Output and I/O Parameters     | 19-20 |

| Timing Characteristics               | 21-41 |

| Operation                            | 42-66 |

| L3M Memory Map                       | 42-43 |

| L3M Register Memory Map Descriptions | 44-63 |

| VCXO                                 | 64-65 |

| Testing                              | 65-66 |

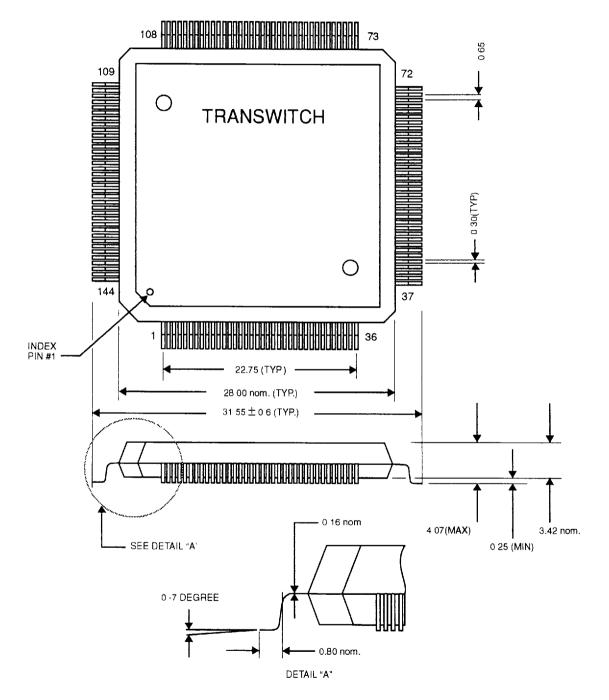

| Packaging                            | 67    |

| Ordering Information                 | 68    |

| Related Products                     | 68    |

| List of Data Sheet Changes           | 69    |

|                                      |       |

L3M

\_ . . . . \_ \_

- --

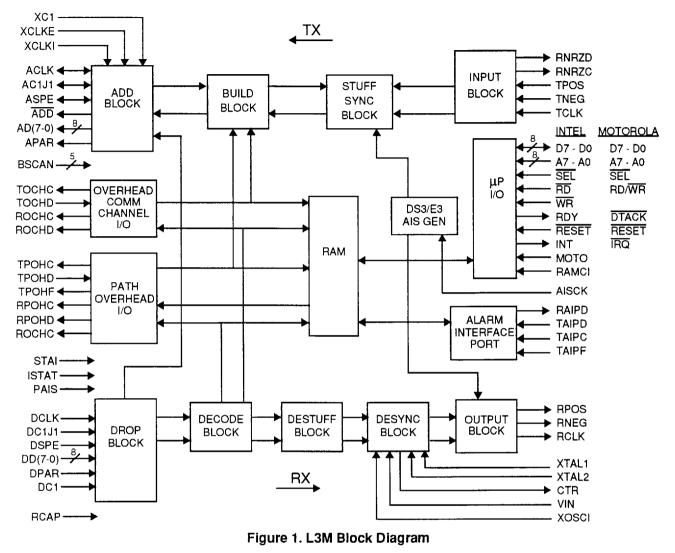

**BLOCK DIAGRAM**

# **BLOCK DIAGRAM DESCRIPTION**

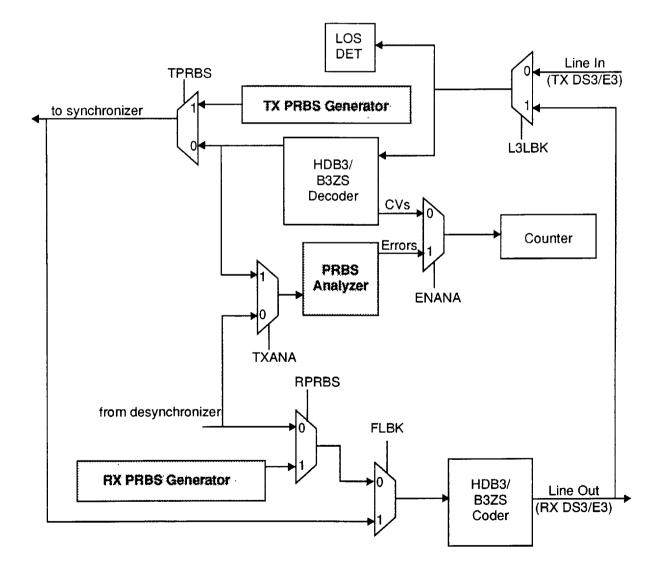

A simplified block diagram of the L3M is shown in Figure 1. A 44.736 (DS3) or 34.368 (E3) Mbit/s NRZ or a Positive/Negative rail clock and data signal is connected to the Input Block. The transmit line input is independent of the receiver, and consists of positive rail/NRZ signal lead (TPOS), negative rail signal lead (TNEG), and input clock (TCLK). A control bit is provided in software that inverts the clock signal if required. The Input Block performs either a HDB3 or B3ZS decoder function if the input line termination is a rail signal. Separate NRZ data (RNRZD) and clock (RNRZC) signals are provided for external performance monitoring circuits. Illegal coding violations are counted in a 16-bit performance counter. When the line termination is NRZ, the negative rail signal lead (TNEG), can be used to clock illegal coding violations from an external device into the 16-bit performance counter. The transmit signal and clock are both monitored for operation, and alarms reported for failure conditions. Control bits are provided that enable the L3M to send a line AIS when either failure is detected. The Input Block also monitors the line signal for an E3 AIS. The Input block also has a 2<sup>15</sup>-1 or 2<sup>23</sup>-1 pseudo-random test generator for testing.

- 3 -

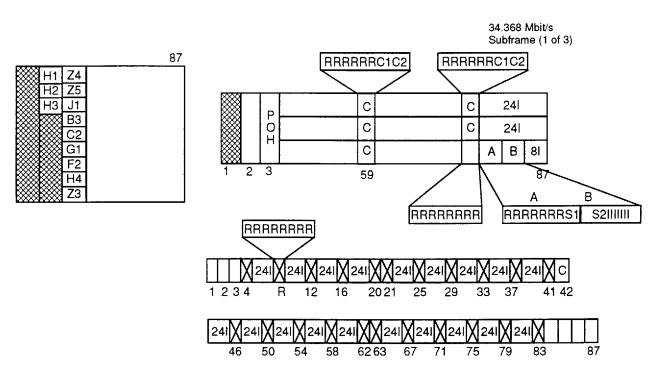

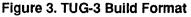

The Stuff/Sync Block and Build Blocks work together for mapping a DS3 or E3 signal into an STS-1 SPE or TUG-3. The mapped formats are shown in Figures 2 and 3. The stuffing algorithm for the DS3 signal format uses one set of five control bits (C-bits) with one stuff opportunity bit (S-bit) for frequency justification, per sub-frame (9 subframes). The E3 format uses two sets of five control bits (C1, C2 bits) to control two stuff opportunity bits (S1 and S2), per subframe (one subframe per three rows for a total of three subframes per frame). A read clock and timing indications are given by the Build Block for reading the transmit FIFO. A FIFO overflow or underflow alarm indication is provided. Should an underflow/overflow condition occur, the FIFO is immediately reset to the start-up preset value. The transmit FIFO also tracks the incoming line signal that can have an average frequency error as high as +/- 20 ppm, and simultaneously accepts this signal with up to 5 UI Peak-to-Peak jitter (where UI = 1/f).

|     |    |    |     |    |      |    |    | 44 736 Mbit/s<br>Subframe (1 o | f 9) |    |    |          |      |

|-----|----|----|-----|----|------|----|----|--------------------------------|------|----|----|----------|------|

| РОН | 8R | 8R | RRC | 51 | 2001 | 8R | 8R | CCRRRRRR                       | 2081 | 8R | 8R | CCRROORS | 2081 |

| 1   | 2  | 3  |     |    |      | 30 | 31 | 32                             |      | 59 | 60 | 61       | 87   |

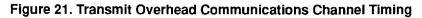

The Build Block, with signals exchanged between itself and the Stuff/Sync Block, constructs one of two 87 column by 9 row formats: a CCITT TUG-3 or an STS-1 (for STS-3) signal. A fixed pointer value of 6800H is used when building a CCITT TUG-3 format. Please note that, when the CCITT TUG-3 mode is selected, the pointer value will change when there is a pointer increment or decrement. However, this feature may be disabled. An O-bit serial interface, or two bits in RAM are used for mapping the two "O" bits into the DS3 SONET format subframes. The O-bit interface consists of an output clock (TOCHC) and an input data lead (TOCHD). The

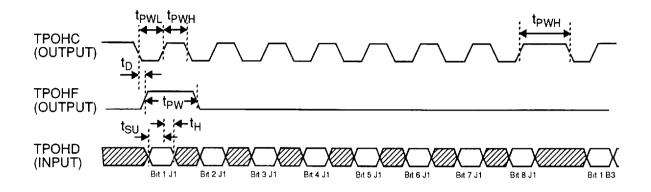

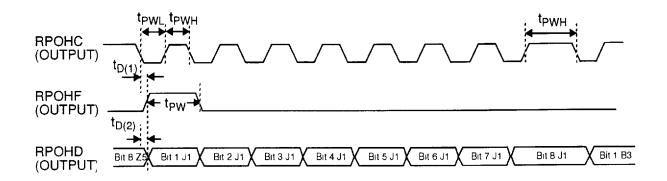

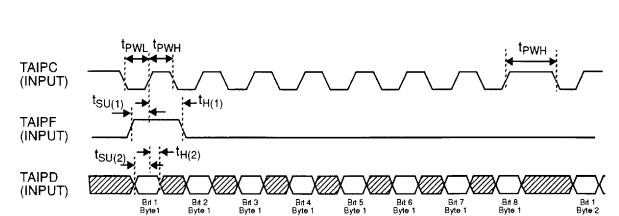

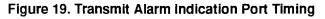

nine Path Overhead bytes are mapped individually into the SONET format from either the POH interface (except the B3 byte), from microprocessor written RAM positions, or from internal logic (such as the path RDI state in bit 5 of G1). The POH interface consists of an output clock (TPOHC), and framing pulse (TPOHF), and an input data lead (TPOHD). A control bit enables the POH interface bytes to be written into RAM when transmitted. Enable bits are provided for controlling the FEBE and path RDI states as a result of local alarms or remote status information received during ring operation. A B3 test mask or fixed byte can also be transmitted. Control bits are provided for generating a TUG-3 path AIS, or an unequipped status condition (payload and POH bytes are equal to zero). An alarm interface provides a FEBE, and path FERF input indication from a mate L3M for ring operation. The alarm interface leads consist of input data (TAIPD), framing pulse (TAIPF), and clock signal (TAIPC).

The Add Block uses an external byte rate clock signal (XCLKI), or the Add or Drop bus clock, SPE and C1J1 timing signals for building and adding a TUG-3, STS-3/STS-1 SPE, or STS-1 SPE to the Add bus. The Add Block supports the STM-1/STS-3 bus signal rate of 19.44 MHz and the STS-1 signal rate of 6.48 MHz. The external clock is enabled by placing a high on the external clock enable lead (XCLKE), and is intended for STS-1 operation. The external clock generates the bus clock (ACLK), C1J1 indication (AC1J1), and SPE indication (ASPE). The output data to the bus is 3-state, active true. A software control bit enables the transport overhead A1, A2, C1, and H1/H2 bytes to be generated. The H1 and H2 bytes will carry the value of 6800 hex and the C1 byte carries the value of 01 hex. An optional C1 signal (XC1 signal lead) can be applied to the L3M to align the start of the frame (A1, A2 bytes).

When add bus timing is selected, the clock (ACLK), C1J1 indication (AC1J1), and SPE indication (ASPE) become input signals from the add bus. When Drop timing is selected, the L3M supports DC1J1 pointer movements on the Drop bus, and adjusts the pointer value in the TUG-3s accordingly. An active low Add indicator is also provided to indicate the location of all time slots that are added to the bus (e.g. TUG-3 A, B or C) by the L3M. The selected clock is monitored for operation, and an odd parity signal (APAR) is calculated for the bus data including the SPE and C1J1 signals when these signals are outputs (e.g. external timing mode).

The Drop Block supports the STM-1/STS-3 bus signaling rate of 19.44 MHz and the STS-1 signal rate of 6.48 MHz. The Drop Block uses the clock (DCLK), C1J1 indication (DC1J1) (and a separate DC1 signal if required), and SPE indication (DSPE) from a Drop bus for determining the location of the Path overhead J1 byte in the VC-4, the three J1 bytes in the three STS-1 SPEs in the STS-3 signal, and the single SPE for STS-1 operation. The C1 pulse is required, and is synchronous with the first C1 byte in the STM-1 Section Overhead bytes, STS-3, or STS-1 Transport Overhead Bytes. The C1 pulse provides a framing indication for determining the location of the E1 byte corresponding to the TUG-3 or STS-1 selected, and is also used by the desynchronizer as a frame reference. The C1 pulse can be present in the DC1J1 signal or provided as a separate signal (DC1). The Drop SPE (DSPE) is active during the POH and payload byte times. The Drop Bus clock, and composite C1J1 signal are monitored for operation, and odd parity calculated and compared against the incoming parity bit.

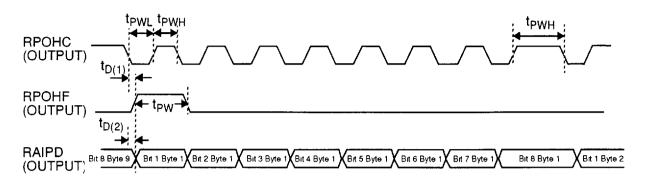

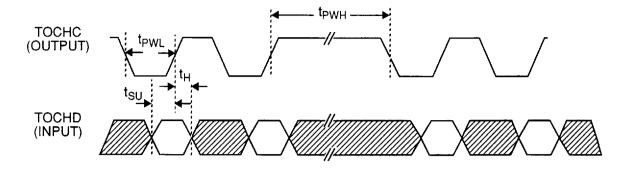

The Decode Block contains the logic for performing pointer justification for the selected TUG-3 signal, removing the Path Overhead bytes, and Overhead Communication bits, and the detection of the E1 byte for an upstream AIS detection. The E1 byte carries an AIS indication from the SOT-3 or SOT-1 device. The SOT-3 (and SOT-1) generates an AIS signal in each of the three E1 bytes (corresponding to the three STS-1s/TUG-3s) when a loss of frame, loss of pointer, loss of signal, or line AIS detected. This indication is used by L3M to generate a Path RDI indication, and for generating a received DS3 or E3 AIS. In place of the E1 byte AIS, the L3M also supports an alarm indication provided on the ISTAT and PAIS signal leads. The TUG-3 pointer is monitored for loss of pointer, New Data Flag, and Path AIS. Performance counters are provided for monitoring pointer movements. All POH bytes are written into RAM locations and are also provided at the POH interface. The POH interface consists of an output data lead (RPOHD), framing pulse (ROCHF), and clock signal (TPOHC). The L3M also provides a microprocessor written location for performing C2 mismatch detection, and unequipped detection based on ANSI and CCITT standards. The received O-bits are available at an external interface and a 2-bit RAM location updated each frame. The O-bit interface consists of a data lead (ROCHD), and clock signal (ROCHC). An alarm indication port is provided for ring operation. The alarm indication port

- 5 -

consists of a data lead (RAIPD), and the POH interface framing pulse (ROCHF), and clock signal (ROCHC). The signal on the data lead (RAIPD) consists of the FEBE count and a path RDI status indication.

The De-Synchronize Block removes the effect on the output DS3 or E3 signals of systemic jitter due to signal mapping and pointer movements. The output is an average frequency equal to the source frequency, and has jitter characteristics that meet CCITT and ANSI standards. The De-Synchronize Block consists of two circuits, a Pointer Leak Block, and a Digital Phase Locked Loop Block. The function of the Pointer Leak Block is to absorb the immediate effect of up to eight consecutive pointer movements (any combination of SPE or TUG-3 pointer movements) in either direction, and filter them out in time. A single pointer adjustment is an 8 Unit Interval (UI) phase step. The Pointer Leak Block turns the phase step into eight 1 UI steps, widely spaced in time, allowing the Phase Lock Loop block to track. In normal operation, the output is one data bit and one clock cycle for each input bit. When a negative stuff occurs 8 extra bits are pulled from the signal and absorbed. Following this operation, the normal operation of one bit in for one bit out continues except that one extra bit is pulled from the FIFO every n frames. In this way, the pointer step is leaked out in 8 x n frames. The value of n is programmed via the microprocessor.

The output block provides either a positive (RPOS) and negative rail (RNEG) line signal or NRZ signal (RPOS), and a clock signal (RCLK). The HDB3/B3ZS coder operates independent of the transmitter. For interface flexibility, a control bit is provided for inverting the output clock. The receive data and clock outputs can be forced to a high impedance state for the purpose of tying two L3M chips together for ring operation, or redundancy. An additional 2<sup>15</sup>-1 or 2<sup>23</sup>-1 pseudo-random test generator is provided. The Output Block and the Input Block share a 2<sup>15</sup>-1 or 2<sup>23</sup>-1 analyzer that can compare the desynchronizer output or transmit data against a fixed pattern. An alarm is provided when the analyzer and incoming data are not synchronous. Errors are counted in the 16-bit coding violation counter. Loopbacks between the Input and Output blocks facilitate board and network debugging.

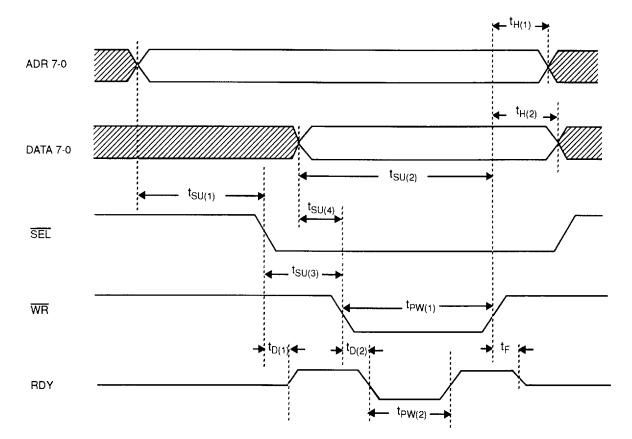

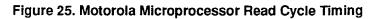

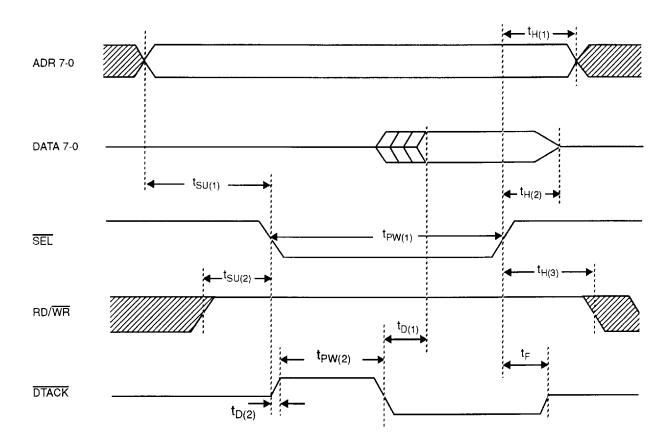

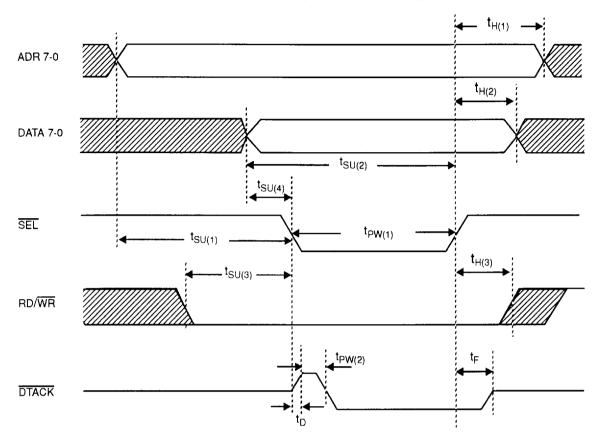

All of the control registers, performance counters, status and alarm indications are accessible through the L3M microprocessor bus interface. The L3M supports both an Intel and Motorola microprocessor bus interface, with both hardware and software interrupt capability. The Motorola compatible microprocessor interface is selected by placing a high on the MOTO signal lead.

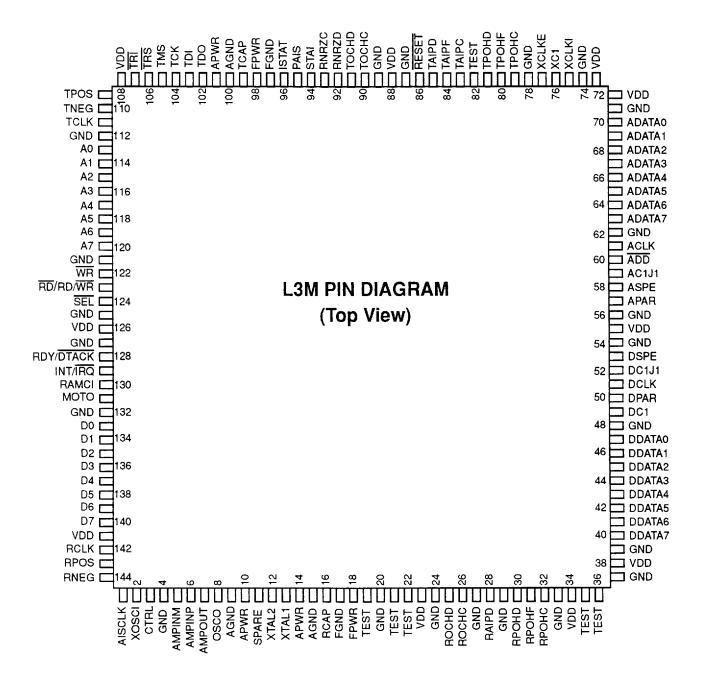

### **PIN DIAGRAM**

Figure 4. L3M Pin Diagram

90041520000626909 🔳

# **PIN DESCRIPTIONS**

# Power Supply and Ground:

| Symbol | Pin No.                                                                                   | I/O/P* | Туре | Name/Function                       |  |

|--------|-------------------------------------------------------------------------------------------|--------|------|-------------------------------------|--|

| VDD    | 23,34,38,55,<br>72,73,88,<br>108,126,141                                                  | Р      |      | VDD: +5 volt supply voltage, +/- 5% |  |

| GND    | 4,20,24,27,<br>29,33,37,39,<br>48,54,56,62,<br>71,74,78,87,<br>89,112,121,<br>125,127,132 | Р      |      | Ground.                             |  |

| SPARE  | 11                                                                                        |        |      | Spare: No connection.               |  |

\*Note: I = Input; O = Output; P = Power

#### Line Interface

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNRZD  | 92      | 0     | CMOS4mA | <b>Receive Line NRZ Data:</b> Additional output provided<br>for an optional external performance monitoring cir-<br>cuit. This serial encoded NRZ output is provided after<br>the decoder (transmit direction) independent of<br>whether the input is NRZ or rail. Data is clocked out on<br>positive transitions of clock (RNRZC). This lead goes<br>to a high impedance state when control bit L3Z is writ-<br>ten with a 1. |

| RNRZC  | 93      | 0     | CMOS4mA | <b>Receive Line Clock:</b> NRZ data on lead RNRZD is clocked out of the L3M on positive transitions of this clock. This lead goes to a high impedance state when control bit L3Z is written with a 1.                                                                                                                                                                                                                          |

| TPOS   | 109     | 1     | CMOS    | Transmit NRZ Line Data/Positive Rail Data: Serial<br>NRZ input for the 44.736 or 34.368 Mbit/s asynchro-<br>nous line data. This lead also provides the positive rail<br>data input for an internal decoder.                                                                                                                                                                                                                   |

| TNEG   | 110     | 1     | CMOS    | Transmit Negative Rail Data: This lead provides a negative rail input for the internal decoder. In the NRZ mode, this lead can be used as an input for counting the number of coding violations from an external line interface device. The decoder coding violation counter is used. When this pin is not used, it should be grounded.                                                                                        |

| TCLK   | 111     | ł     | CMOS    | Transmit Line Clock: NRZ or rail data is clocked into<br>the L3M using the TPOS/TNEG signal leads on posi-<br>tive transitions of this clock when control bit INVCI is 0.<br>NRZ or rail data is clocked in on negative transitions<br>when control bit INVCI is a 1.                                                                                                                                                          |

Draft: August 12, 1993

- -

TXC-03452-MB Ed. 2, November 1993

# PRODUCT PREVIEW

| Symbol | Pin No. | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|---------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK   | 142     | 0     | CMOS4mA | <b>Receive Line Clock:</b> Line data present on the RPOS/<br>RNEG signal leads (44.736 or 34.368 Mbit/s) is<br>clocked out of the L3M on negative transitions of this<br>clock when control bit INVCI is 0. NRZ or rail data is<br>clocked out on positive transitions of this clock when<br>control bit INVCO is written with a 1. This lead goes to<br>a high impedance state when control bit L3Z is equal<br>to 1. |

| RPOS   | 143     | 0     | CMOS4mA | Receive Line NRZ Data/Positive Rail Data: Serial<br>NRZ output for the 44.736 or 34.368 Mbit/s asynchro-<br>nous line data. This lead also provides the positive rail<br>output when the rail interface is selected. This lead<br>goes to a high impedance state when control bit L3Z is<br>equal to 1.                                                                                                                |

| RNEG   | 144     | 0     | CMOS4mA | <b>Receive Negative Rail Data:</b> This lead provides a negative rail interface from the internal coder. This lead goes to a high impedance state when control bit L3Z is equal to 1. When the NRZ interface is selected, this lead is unused.                                                                                                                                                                         |

# Microprocessor Interface

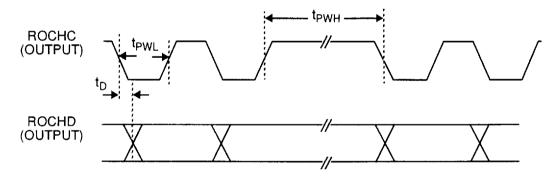

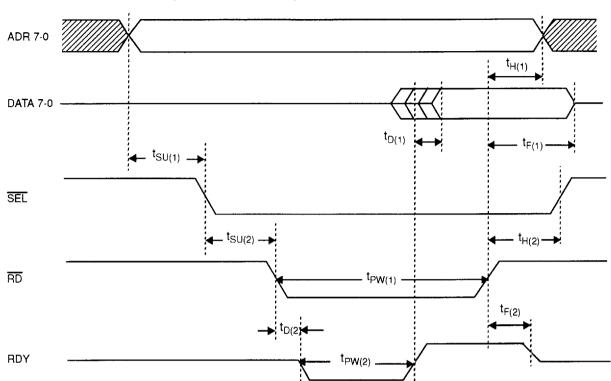

| Symbol        | Pin No.   | I/O/P        | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-----------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(7-0)        | 120 - 113 | I            | TTL    | Address Bus: These are active high address line<br>inputs that are used by the microprocessor for access-<br>ing an L3M RAM location for a read/write cycle. A0 is<br>the least significant bit.                                                                                                                                                                                                                                                                                                                |

| WR            | 122       | Ι            | ΠL     | Write (I mode): Intel Mode - An active low signal gen-<br>erated by the microprocessor for writing to the L3M<br>RAM locations. Motorola Mode - Not used.                                                                                                                                                                                                                                                                                                                                                       |

| RD/WR         | 123       | I            | ΤΤL    | Read (I mode) or Read/Write (M mode): Intel Mode -<br>An active low signal generated by the microprocessor<br>for reading the L3M RAM locations. Motorola Mode -<br>An active high signal generated by the microprocessor<br>for reading the L3M RAM locations. A low signal is<br>used to write to L3M RAM locations.                                                                                                                                                                                          |

| SEL           | 124       | 1            | T⊤Lp   | Select: A low enables data transfers between the microprocessor and the L3M during a read/write cycle.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RDY/<br>DTACK | 128       | O<br>3-state | TTL8mA | Ready (I mode) or Data Transfer Acknowledge (M<br>mode): Intel Mode - A high is an acknowledgment<br>from the addressed RAM location that the transfer can<br>be completed. A low shall indicate that the L3M cannot<br>complete the transfer cycle, and microprocessor wait<br>states must be generated. Motorola Mode - During a<br>read bus cycle, a low signal shall indicate the informa-<br>tion on the data bus is valid. During a write bus cycle,<br>a low signal acknowledges the acceptance of data. |

TXC-03452-MB Ed. 2, November 1993

L3M

# PRODUCT PREVIEW

| Symbol  | Pin No.   | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT/ĪRQ | 129       | 0     | TTL4mA | Interrupt: Intel Mode - A high on this output pin sig-<br>nals an interrupt request to the microprocessor. Motor-<br>ola Mode - A low on this pin signals an interrupt<br>request for the microprocessor.                                                                                                                                                                                       |

| RAMCI   | 130       | 1     | CMOS   | <b>RAM Clock Input:</b> Clock input for the internal RAM.<br>This clock allows an outside clock to provide an arbi-<br>trator function for accessing the internal RAM struc-<br>ture. This clock has an operating rate between 12 and<br>25 MHz and a duty cycle of +/- 10 percent. This clock<br>and microprocessor timing signals may operate asyn-<br>chronously with respect to each other. |

| мото    | 131       | B     | ΠL     | Motorola/Intel Microprocessor Select: A high selects the Motorola microprocessor compatible bus interface. A low selects the Intel microprocessor compatible bus interface.                                                                                                                                                                                                                     |

| D(7-0)  | 140 - 133 | I/O   | TTL8mA | <b>Data Bus:</b> Bi-directional data lines used for transfer-<br>ring data between the L3M and an external processor.<br>D0 is the least significant bit.                                                                                                                                                                                                                                       |

## **Drop Bus Interface**

| Symbol         | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDATA<br>(7-0) | 40 - 47 | I     | TTL  | <b>Drop Data Byte:</b> Byte data that corresponds to the STM-3/STS-3/STS-1 signal from the drop bus. The first bit received corresponds to bit 7.                                                                                                                                                                                                            |

| DC1            | 49      | 1     | TTL  | <b>Drop C1 Pulse:</b> External positive C1 pulse that may be provided on this pin instead of in the DC1J1 signal. This signal is ORed internally with the DC1J1 signal to form a composite C1J1 signal. If this lead is not used it must be grounded.                                                                                                        |

| DPAR           | 50      | I     | TTL  | <b>Drop Bus Parity Bit:</b> This is an odd parity input for each data byte, the DSPE signal, and the composite DC1J1 pulses.                                                                                                                                                                                                                                 |

| DCLK           | 51      | 1     | TTL  | <b>Drop Bus Clock:</b> This clock operates at 19.44 MHz<br>for STM-1/STS-3 operation, and 6.48 MHz for STS-1<br>bus operation. Drop bus byte wide data (DDATA7-0),<br>parity (DPAR), payload indicator (DSPE), and C1/J1<br>(DC1J1 and DC1) are clocked into the L3M on nega-<br>tive transitions of this clock.                                             |

| DC1J1          | 52      | I     | TTL  | <b>Drop Bus C1 and J1 Indicator:</b> The C1 pulse is an active high, one clock cycle wide timing pulse that indicates the location of the first C1 time slot in the STM-1 or STS-3 frame. If the C1 pulse is not present in this signal, it must be provided at the DC1 lead. A J1 pulse, also one clock cycle wide, identifies the location of the J1 byte. |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                               |

|--------|---------|-------|------|-------------------------------------------------------------------------------------------------------------|

| DSPE   | 53      |       |      | <b>Drop Bus SPE Indicator:</b> A signal that is high during the STM-1 VC-4, and the STS-3/STS-1 SPE period. |

### Add Bus Interface

| Symbol | Pin No. | I/O/P          | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APAR   | 57      | O<br>3-state   | TTL4mA | Add Bus Parity Bit: This output bit represents the<br>odd parity calculation for each data byte in the add<br>timing and drop timing modes. In the external timing<br>mode, the parity calculation also includes the ASPE<br>and AC1J1 signals which become outputs. This lead<br>is forced to a high impedance state when the control<br>bit ADDZ is written with a 1, or when ADD is inactive<br>(high).                                                                                           |

| ASPE   | 58      | I/O<br>3-state | TTL4mA | Add Bus SPE Indicator: An input signal that is active<br>high during the STM-1 VC-4 period, and STS-3/STS-<br>1 SPE period. When enabled by the external clock<br>enable (XCLKE) control pin, this signal becomes an<br>output. This lead is forced to a high impedance state<br>when the control bit ADDZ is written with a 1, or when<br>the drop timing mode is selected.                                                                                                                         |

| AC1J1  | 59      | I/O<br>3-state | TTL4mA | Add Bus C1 and J1 Indicator: The C1 pulse is an active high, one clock cycle wide input timing pulse that identifies the location of the first C1 time slot in the STM-1 or STS-3 frame. A J1 pulse, also one clock cycle wide, identifies the location of the J1 byte. When enabled by the external clock enable (XCLKE) control pin, this signal becomes an output. This lead goes to a high impedance state when control bit ADDZ is written with a 1, or, when the drop timing mode is selected. |

| ADD    | 60      | O<br>3-state   | TTL4mA | Add Indicator: An active low signal that identifies the position of the data time slots being mapped onto the add bus. The time slots may be fixed stuff or data, as determined by the L3M. This lead is forced to the high impedance state when the control bit ADDZ is written with a 1.                                                                                                                                                                                                           |

| ACLK   | 61      | I/O            | TTL4mA | Add Bus Clock: This clock operates at 19.44 MHz<br>for STM-1/STS-3 operation, and at 6.48 MHz for STS-<br>1 bus operation. The add clock is used for build timing<br>and for sourcing the add bus byte wide data (AD7-0),<br>parity (APAR), and add indicator. When enabled by<br>the external clock enable (XCLKE) control lead, this<br>signal becomes an output. This lead goes to a high<br>impedance state when control bit ADDZ is written with<br>a 1.                                        |

# PRODUCT PREVIEW

| Symbol         | Pin No. | I/O/P        | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                     |

|----------------|---------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADATA<br>(7-0) | 63 - 70 | O<br>3-state | TTL4mA | Add Data Byte: Byte-wide data that corresponds to<br>the STM-3/STS-3/STS-1 time slots that are placed on<br>the add bus. Bit 7 corresponds to bit 1 in the STM-1/<br>SONET transmission format. This bus is forced to a<br>high impedance state when the control bit ADDZ is<br>written with a 1, or when ADD is inactive (high). |

### **Overhead Comm Channel Interface**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                       |

|--------|---------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROCHD  | 25      | 0     | TTL4mA | <b>Receive Overhead Comm Channel Data:</b> Unaligned data output for the overhead communications channel O-bits from the DS3 format. The O-bits are clocked out of the L3M on negative transitions of the ROCHC clock signal.                                                                                       |

| ROCHC  | 26      | 0     | TTL4mA | Receive Overhead Comm Channel Clock: A<br>gapped 720 kHz output clock with an average fre-<br>quency of 144 kHz for outputting the transmit over-<br>head communications channel bits to external<br>circuitry.                                                                                                     |

| тоснс  | 90      | 0     | TTL4mA | Transmit Overhead Comm Channel Clock: A<br>gapped 720 kHz output clock with an average fre-<br>quency of 144 kHz for sourcing the transmit overhead<br>communications channel bits from external circuitry.                                                                                                         |

| TOCHD  | 91      | 1     | TTL    | Transmit Overhead Comm Channel Data: Data<br>input for the overhead communications channel in the<br>DS3 format. Data is clocked into the L3M on positive<br>transitions of the TOCHC clock signal. The bits are<br>multiplexed into the O-bit positions unaligned regard-<br>ing bit position and subframe number. |

#### Path Overhead Interface

| Symbol | Pin No. | 1/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOHD  | 30      | 0     | TTL4mA | <b>Receive Path Overhead Data:</b> The serial output for<br>the nine path overhead bytes. The POH bytes are<br>clocked out on negative transitions of the clock signal<br>(RPOHC).                                                                                                                                |

| RPOHF  | 31      | 0     | TTL4mA | <b>Receive Path Overhead Framing:</b> A positive one clock cycle (RPOHC) wide output framing pulse that is synchronous with the J1 byte. This signal is also used as the framing pulse for the receive alarm indication port data (RAIPD).                                                                        |

| RPOHC  | 32      | 0     | TTL4mA | <b>Receive Path Overhead Clock:</b> A gapped clock used for clocking out the path overhead bytes, and receive alarm indication port data (RAIPD).                                                                                                                                                                 |

| ТРОНС  | 79      | 0     | TTL4mA | Transmit Path Overhead Clock: A gapped clock used for clocking the path overhead bytes from an external circuit into the L3M.                                                                                                                                                                                     |

| TPOHF  | 80      | 0     | TTL4mA | <b>Transmit Path Overhead Framing:</b> A positive one clock cycle (TPOHC) wide output framing pulse that determines the start of the J1 byte.                                                                                                                                                                     |

| TPOHD  | 81      | I     | TTL    | <b>Transmit Path Overhead Data:</b> A serial input for the following path overhead bytes: J1, G1, C2, F2, H4, Z3, Z4, and Z5 bytes. The POH bytes are clocked into the L3M on positive transitions of the TPOHC clock signal. Eight bits are clocked in during the B3 byte time, but they are ignored by the L3M. |

### Alarm Indication Port

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAIPD  | 28      | 0     | TTL4mA | Receive Alarm Indication Port Data: A serial output<br>that provides the 4-bit FEBE count (B3 error count)<br>and Path RDI alarm indication to a mate L3M for ring<br>operation. This lead is normally connected to the<br>TAIPD lead at the mate L3M. The RPOHC signal is<br>used to clock this signal out of the L3M. The RPOHF<br>signal provides the frame reference signal. The bits<br>are sent in the following format: |

|        |         |       |        | Bits 1 2 3 4 5 6 7 8                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |         |       |        | B3 Count RDI 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |         |       |        | Bit 1 is the MSB and is sent first in the bit stream.                                                                                                                                                                                                                                                                                                                                                                          |

# PRODUCT PREVIEW

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                          |

|--------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TAIPC  | 83      | I     | TTL  | Transmit Alarm Indication Port Clock: This clock<br>input is normally connected to the RPOHC clock lead<br>at the mate L3M for ring operation. Transmit alarm<br>data (TAIPD) is clocked into the L3M on positive tran-<br>sitions of the RPOHC clock. |

| TAIPF  | 84      | I     | TTL  | Transmit Alarm Indication Port Framing Pulse:<br>Normally connected to RPOHF lead at the mate L3M<br>for ring operation. Used to indicate the first bit in the<br>first byte for the external alarm indications.                                       |

| TAIPD  | 85      | I     | TTL  | Transmit Alarm Indication Port Data: This serial<br>input lead is normally connected to the RAIPD lead at<br>the mate L3M for ring operation. Provides an input for<br>the four bit FEBE count (B3 error count), and Path<br>RDI alarm indication.     |

# Additional Signals

| Symbol | Pin No.         | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                             |

|--------|-----------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AISCLK | 1               | Ι     | CMOS | AIS Clock Input: Clock input for the L3M AIS gener-<br>ator. This clock must be present in order for the AIS<br>generator to function. The clock must have the oper-<br>ating line rate of either 44.736 or 34.368 MHz, and<br>have a frequency stability of at least +/- 20 ppm.                         |

| TEST   | 21,22,<br>35,36 |       |      | TranSwitch Test Pins: No connections; do not use.                                                                                                                                                                                                                                                         |

| XCLKI  | 75              | I     | CMOS | External Clock Input: Used to derive output timing<br>and data for the add bus. Enabled by placing a high<br>on the lead labeled XCLKE. A byte clock frequency of<br>6.48 MHz is required for STS-1 operation. This clock<br>is monitored for loss of clock when the external timing<br>mode is selected. |

| XC1    | 76              | 1     | TTL  | External C1 Input: Optional C1 input signal used to synchronize the frame start when the external timing mode is selected for the add bus.                                                                                                                                                                |

| XCLKE  | 77              | 1     | TTL  | <b>External Clock Enable:</b> A high on this lead enables<br>add bus timing to be derived from the XCKLI lead<br>(external clock signal). The ASPE, AC1J1, and ACLK<br>signal leads become output leads.                                                                                                  |

| RESET  | 86              | Ι     | TTLp | Hardware Reset: A low clears all counters and data-<br>paths. This pin is provided with an internal pull-up<br>resistor. The reset signal must be low for a minimum<br>of 200 nanoseconds. The bus clocks and VCXO<br>clocks must be present.                                                             |

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                  |

|--------|---------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STAI   | 94      | I     | TTL  | STS Network Alarm Indication: A high on this lead<br>will generate a count of 9 in bits 1 through 4 of G1<br>when control bit FEBE9EN is equal to 1. An indication<br>is also provided as the XSTAI alarm.                                                                                                                                                     |

| PAIS   | 95      | ŀ     | TTL  | External Path AIS Indication: A high on this lead<br>indicates an external Path AIS has occurred. An indi-<br>cation is also provided as the XPAIS alarm. The alarm<br>actions taken by this pin are enabled when a 1 is writ-<br>ten to control bit XALM2AIS. When enabled, the<br>alarm actions taken by detecting an AIS in the E1<br>byte are disabled.    |

| ISTAT  | 96      | I     | TTL  | External STS-1 Alarm Indication: A high on this<br>lead indicates an external SONET alarm has<br>occurred. An indication is also provided as the<br>XISTAT alarm. The alarm actions taken by this pin are<br>enabled when a 1 is written to control bit XALM2AIS.<br>When enabled, the alarm actions taken by detecting<br>an AIS in the E1 byte are disabled. |

| TRI    | 107     | I     | ΤΤLp | High Impedance Enable: A low causes all L3M out-<br>puts and bi-directional pins to a high impedance state<br>for test purposes. This pin is provided with an internal<br>pull-up resistor.                                                                                                                                                                    |

### Receive and Transmit Phase Locked Loops

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                               |

|--------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------|

| RCAP   | 16      | Ι     | Analog | Receiver Internal Phase Locked Loop Capacitor:<br>Optional capacitor used for an internal receive phase<br>lock loop.       |

| TEST   | 19      | I/O   |        | TranSwitch Test for Receive PLL: Do not use.                                                                                |

| TEST   | 82      | 1/0   |        | TranSwitch Test for Transmit PLL: Do not use                                                                                |

| TCAP   | 99      | I     | Analog | Transmitter Internal Phase Locked Loop Capaci-<br>tor: Optional capacitor used for an internal transmit<br>phase lock loop. |

# **Receive Desynchronizer**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                         |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

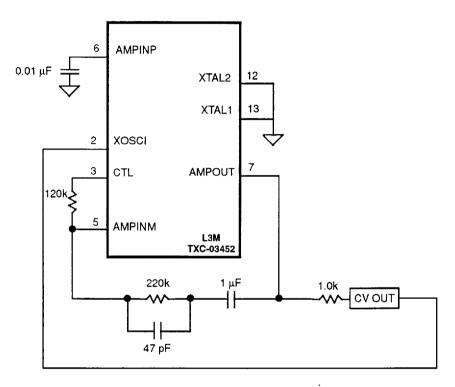

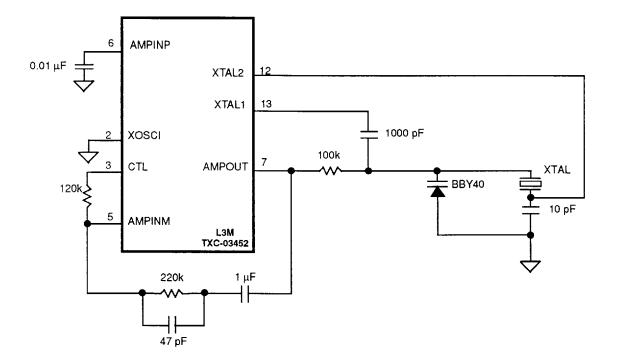

| XOSCI  | 2       | Ι     | CMOS | <b>External Oscillator Input:</b> This input is connected to the output of the external VCXO, as shown in the VCXO application in this data sheet. The external VCXO is selected by writing a 1 to control bit XVCXO. |

\_ \_\_ \_\_\_

# PRODUCT PREVIEW

| Symbol | Pin No.   | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------|-----------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CTRL   | 3         | 0     | TTL8mA  | Phase Detector Output: Normally connected to the external low pass filter consisting of external components and the internal amplifier.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| AMPINM | 5         | I     | Analog  | Low Pass Filter Internal Amplifier - Negative Pol<br>Input: Negative port of an internal amplifier which is<br>used as a low pass filter.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| AMPINP | 6         | ļ     | Analog  | Low Pass Filter Internal Amplifier - Positive Port<br>Input: Positive port of an internal amplifier which is<br>used as a low pass filter.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| AMPOUT | 7         | 0     | Analog  | Low Pass Filter Internal Amplifier, Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| OSCO   | 8         | 0     | CMOS4mA | Internal VCXO Oscillator Output: Internal VCXO oscillator output provided for testing purposes only.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| XTAL2  | 12        | 1     | CMOS    | Internal VCXO Crystal Input: Required if the internative VCXO is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| XTAL1  | 13        |       | CMOS    | Internal VCXO Crystal Input: Required if the internal<br>VCXO is used. The following are the crystal charac-<br>teristics:<br>DS3:<br>Mode: Fundamental, parallel redundant<br>Frequency: 44736000 Hz<br>Cm: 22fF $\pm$ 10%<br>Rm: < 20 ohms<br>CI: 10.5 pF<br>Tolerance: $\pm$ 50 ppm<br>Drive Level: 500 $\mu$ W RMS<br>E3:<br>Mode: Fundamental, parallel redundant<br>Frequency: 34368000 Hz (E3)<br>Cm: 20 fF $\pm$ 10%<br>Rm: < 20 ohms<br>CI: 10.5 pF<br>Tolerance: $\pm$ 60 ppm<br>Drive Level: 500 $\mu$ W RMS |  |  |

| APWR   | 10,14,101 | Р     |         | Analog VDD: +5 Volts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| AGND   | 9,15,100  | Р     |         | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| FPWR   | 18,98     | Ρ     |         | Analog VDD2: +5 Volts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| FGND   | 17,97     | Р     |         | Analog Ground2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

TRAN גאללע. Ζ

.

L3M

**Boundary Scan Testing**

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDO    | 102     | 0     | TTL4mA | Boundary Scan Data Output: Serial data clocked out on negative transitions of TCK.                                                                                                                                                                                                                                                                               |

| TDI    | 103     |       | TTL    | Boundary Scan Data Input: Serial data input for boundary scan test messages.                                                                                                                                                                                                                                                                                     |

| тск    | 104     | 1     | TTL    | <b>Boundary Scan Clock:</b> The input clock for boundary scan testing. The TDI and TMS states are clocked in on positive transitions.                                                                                                                                                                                                                            |

| TMS    | 105     | ļ     | TTL    | Boundary Scan Mode Select: The signal present on this lead is used to control test operations.                                                                                                                                                                                                                                                                   |

| TRS    | 106     | Ι     | ΤΤĻρ   | <b>Boundary Scan Reset:</b> When a low signal is applied to this pin, the L3M Test Access Port (TAP) controller resets, and the boundary scan capability is disabled. The controller is also reset by holding the TMS signal lead high for at least five rising clock transitions of TCK. When the boundary scan feature is not used, this pin must be held low. |

---- - -----

# **ABSOLUTE MAXIMUM RATINGS\***

| Parameter                      | Symbol          | Min  | Мах                   | Unit  |

|--------------------------------|-----------------|------|-----------------------|-------|

| Supply voltage                 | V <sub>DD</sub> | -0.3 | 7.0                   | V     |

| DC input voltage               | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Continuous power dissipation   | P <sub>C</sub>  |      | 0.5                   | Watts |

| Ambient operating temperature  | T <sub>A</sub>  | -40  | 85                    | °C    |

| Operating junction temperature | Т <sub>Ј</sub>  |      | 125                   | °C    |

| Storage temperature range      | T <sub>S</sub>  | -55  | 125                   | °C    |

\*Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

### THERMAL CHARACTERISTICS

| Parameter                     | Min | Тур | Max | Unit | Test Conditions |

|-------------------------------|-----|-----|-----|------|-----------------|

| Thermal res - junc to ambient |     |     | 34  | °C/W |                 |

| Thermal res - junc to case    |     | 12  |     | °C/W |                 |

### POWER REQUIREMENTS

| Parameter                | Min  | Тур | Max   | Unit | Test Conditions  |

|--------------------------|------|-----|-------|------|------------------|

| V <sub>DD</sub>          | 4.75 | 5   | 5.25  | V    |                  |

| l <sub>DD</sub>          |      |     | 190   | mA   |                  |

| P <sub>DD</sub>          |      |     | 997.5 | mW   | Inputs switching |

| Analog V <sub>DD</sub>   | 4.75 | 5   | 5.25  | V    |                  |

| Analog I <sub>DD</sub>   |      |     | 30    | mA   |                  |

| Filtered V <sub>DD</sub> | 4.75 | 5   | 5.25  | V    |                  |

| Filtered I <sub>DD</sub> |      |     |       |      |                  |

# INPUT, OUTPUT, AND I/O PARAMETERS

## **Input Parameters For CMOS**

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions                   |

|-----------------------|------|-----|------|------|-----------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | $4.75 \le V_{\text{DD}} \le 5.25$ |

| V <sub>IL</sub>       |      |     | 1.65 | V    | $4.75 \le V_{DD} \le 5.25$        |

| Input leakage current |      |     | 10   | μA   | V <sub>DD</sub> = 5.25            |

| Input capacitance     |      | 3.5 |      | pF   |                                   |

### Input Parameters For TTL

| Parameter             | Min                                    | Тур       | Max | Unit | Test Conditions                             |

|-----------------------|----------------------------------------|-----------|-----|------|---------------------------------------------|

| V <sub>IH</sub>       | 2.0                                    | · · · · · |     | V    | 4.75 <u>≤</u> V <sub>DD</sub> <u>≤</u> 5.25 |

| V <sub>IL</sub>       | ···· · · · · · · · · · · · · · · · · · |           | 0.8 | V    | $4.75 \le V_{DD} \le 5.25$                  |

| Input leakage current |                                        |           | 10  | μΑ   |                                             |

| Input capacitance     |                                        | 3.5       |     | pF   |                                             |

### Input Parameters For TTLp

| Parameter             | Min | Тур | Max | Unit | Test Conditions                         |

|-----------------------|-----|-----|-----|------|-----------------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | $4.75 \le V_{\text{DD}} \le 5.25$       |

| V <sub>IL</sub>       |     |     | 0.8 | V    | $4.75 \le V_{DD} \le 5.25$              |

| Input leakage current |     | 0.5 | 1.4 | mA   | V <sub>DD</sub> = 5.25; input = 0 volts |

| Input capacitance     |     | 3.5 |     | pF   |                                         |

### **Output Parameters For CMOS4mA**

| Parameter         | Min                   | Тур | Max  | Unit | Test Conditions                                |

|-------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>OH</sub>   | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>   |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub>   |                       |     | 4.0  | mA   |                                                |

| I <sub>OH</sub>   |                       |     | -4.0 | mA   |                                                |

| t <sub>RISE</sub> | 1.2                   | 2.8 | 5.0  | ns   | C <sub>LOAD</sub> = 15pF                       |

| t <sub>FALL</sub> | 0.9                   | 2.0 | 4.1  | ns   | C <sub>LOAD</sub> = 15pF                       |

### Input/Output Parameters For TTL4mA

| Parameter             | Min                   | Тур | Max  | Unit | Test Conditions                                   |

|-----------------------|-----------------------|-----|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0                   |     |      | V    | $4.75 \le V_{DD} \le 5.25$                        |

| V <sub>IL</sub>       |                       |     | 0.8  | V    | $4.75 \le V_{DD} \le 5.25$                        |

| Input leakage current |                       |     | 10   | μA   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |                       | 3.5 |      | pF   |                                                   |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -2.0 mA |

| V <sub>OL</sub>       |                       |     | 0.4  | Ý V  | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0 mA  |

| I <sub>OL</sub>       |                       |     | 4.0  | mA   |                                                   |

| I <sub>OH</sub>       |                       |     | -2.0 | mA   |                                                   |

| t <sub>RISE</sub>     | 2.5                   | 5.5 | 10.0 | ns   | C <sub>LOAD</sub> = 15pF                          |

| <sup>†</sup> FALL     | 1.0                   | 2.0 | 4.0  | ns   | C <sub>LOAD</sub> = 15pF                          |

# Input/Output Parameters For TTL8mA

| Parameter             | Min                   | Тур | Мах  | Unit | Test Conditions                                   |

|-----------------------|-----------------------|-----|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0                   |     |      | V    | $4.75 \le V_{DD} \le 5.25$                        |

| V <sub>IL</sub>       |                       |     | 0.8  | V    | $4.75 \le V_{DD} \le 5.25$                        |

| Input leakage current |                       |     | 10   | μΑ   | V <sub>DD</sub> = 5.25                            |

| Input capacitance     |                       | 3.5 |      | pF   |                                                   |

| V <sub>OH</sub>       | V <sub>DD</sub> - 0.5 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 mA |

| V <sub>OL</sub>       |                       |     | 0.4  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0 mA  |

| lol                   |                       |     | 8.0  | mA   |                                                   |

| I <sub>OH</sub>       |                       |     | -4.0 | mA   |                                                   |

| t <sub>RISE</sub>     | 1.9                   | 4.5 | 8.0  | ns   | C <sub>LOAD</sub> = 25pF                          |

| tFALL                 | 0.8                   | 1.5 | 3.1  | ns   | C <sub>LOAD</sub> = 25pF                          |

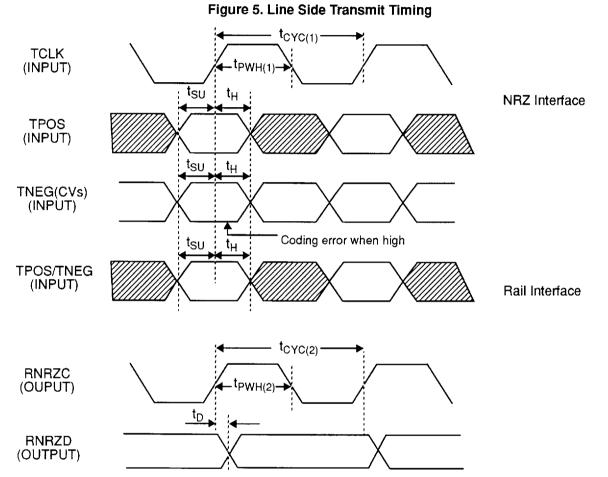

# TIMING CHARACTERISTICS

Detailed timing diagrams for the L3M are illustrated in Figures 5 through 26, with values of the timing intervals following each figure. All output times are measured with a maximum 25 pF load capacitance. Timing parameters are measured at  $(V_{OH} - V_{OL})/2$  or  $(V_{IH} - V_{IL})/2$  as applicable.

Note: Shown for TINVC equal to 0; data is clocked in on the negative edge when TINVC equals 1. RNRZD is always clocked out on the positive transitions of RNRZC. The delay between the input clock TCLK and output clock RNRZC is not specified.

| Parameter                                                    | Symbol              | Min  | Тур | Max | Unit |

|--------------------------------------------------------------|---------------------|------|-----|-----|------|

| TCLK clock period                                            | t <sub>CYC(1)</sub> |      | *   |     | ns   |

| TCLK duty cycle (t <sub>PWH(1)</sub> /t <sub>CYC(1)</sub> )  |                     | 40   | 50  | 60  | %    |

| Input set-up time to TCLK1                                   | t <sub>SU</sub>     | 4.0  |     |     | ns   |

| Input hold time after TCKL1                                  | t <sub>H</sub>      | 2.0  |     |     | ns   |

| RNRZC clock period                                           | t <sub>CYC(2)</sub> |      | *   |     | ns   |

| RNRZC duty cycle (t <sub>PWH(2)</sub> /t <sub>CYC(2)</sub> ) |                     | 40   | 50  | 60  | %    |

| RNRZD output delay after RNRZC1                              | t <sub>D</sub>      | -2.0 |     | 5.0 | ns   |

\* 22.35 ns (DS3) or 29.10 ns (E3).

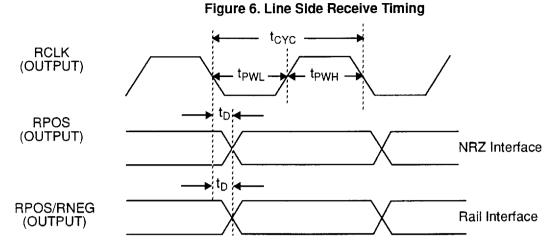

Note: Shown for RINVC equal to 0; data is clocked out on the positive edge when RINVC equals 1. The three signals are forced to a high impedance state when control bit L3Z is written with a 1.

| Parameter                     | Symbol           | Min  | Тур                 | Max | Unit |

|-------------------------------|------------------|------|---------------------|-----|------|

| RCLK clock period             | t <sub>CYC</sub> |      | *                   |     | ns   |

| RCLK high time                | t <sub>PWH</sub> |      | t <sub>CYC</sub> /2 |     | ns   |

| RCLK low time                 | t <sub>PWL</sub> |      | t <sub>CYC</sub> /2 |     | ns   |

| Data output delay after RCLK↓ | t <sub>D</sub>   | -2.0 |                     | 5.0 | ns   |

\*22.35 ns (DS3) or 29.10 ns (E3).

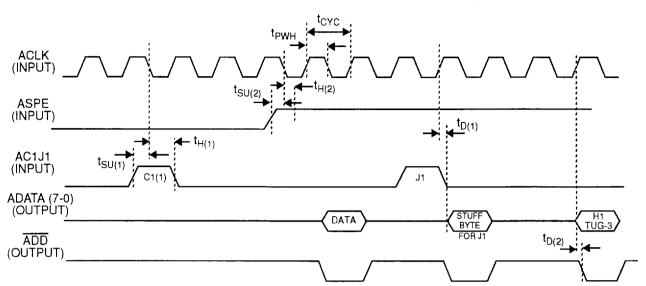

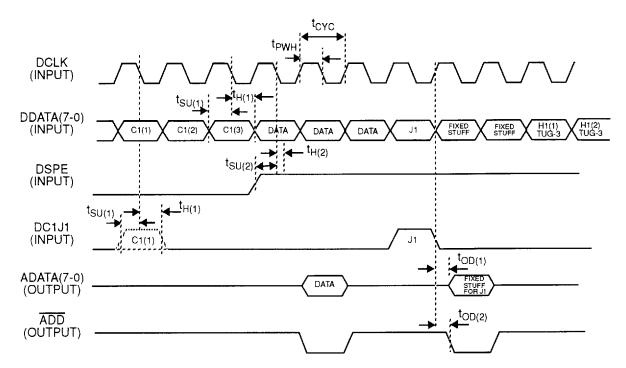

#### Figure 7. STM-1 Add Bus Derived Interface Timing

Note: The relationship between J1 and the SPE signal is shown for illustration purposes only. For the STM-1 format, there will be one J1 pulse which indicates the start of the VC-4 that carries the three TUG-3s. The TUG-3 added to the bus is shown for TUG-3 designated as A. TUG-3 B will occur one clock cycle later.

| Parameter                                             | Symbol             | Min   | Тур   | Max  | Unit |

|-------------------------------------------------------|--------------------|-------|-------|------|------|

| ACLK clock period                                     | t <sub>CYC</sub>   |       | 51.44 |      | ns   |

| ACLK duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                    | 40    | 50    | 60   | %    |

| AC1J1 set-up time to ACLK $\downarrow$                | t <sub>SU(1)</sub> | 7.0   |       |      | ns   |

| AC1J1 hold time after ACLK $\downarrow$               | t <sub>H(1)</sub>  | 3.0   |       |      | ns   |

| ASPE set-up time to ACLK $\downarrow$                 | t <sub>SU(2)</sub> | 10.0  |       |      | ns   |

| ASPE hold time after ACLK↓                            | t <sub>H(2)</sub>  | 5.0   |       |      | ns   |

| Data output delay from ACLK <sup>↑</sup>              | t <sub>D(1)</sub>  | · · · |       | 30.0 | ns   |

| Add low output delay from ACLK <sup>↑</sup>           | t <sub>D(2)</sub>  |       |       | 15.0 | ns   |

**T**RA:

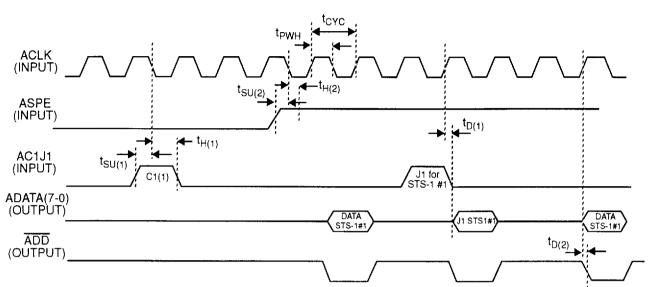

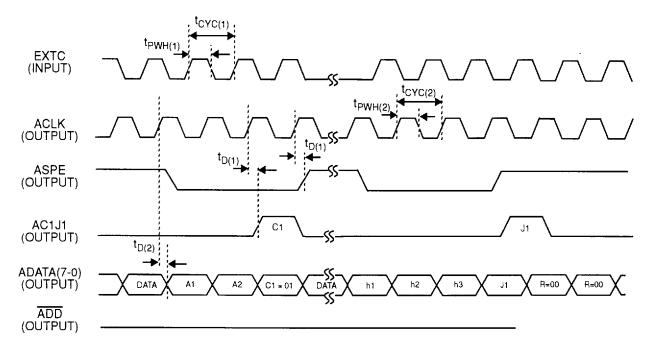

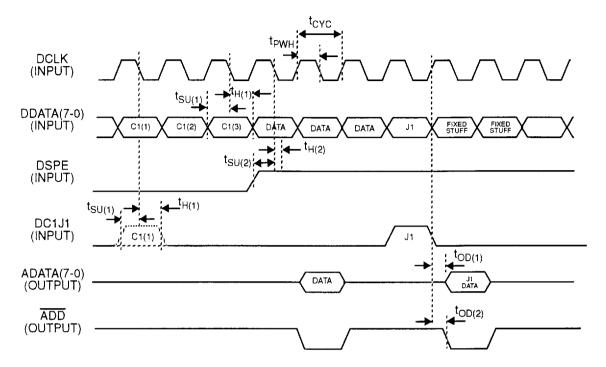

### Figure 8. STS-3 Add Bus Derived Interface Timing

Note: The relationship between J1 and the SPE signal is shown for illustration purposes only. For the STS-3 format, there will be three J1 pulses which indicate the start of each of the STS-1 SPEs. The STS-1 SPE added to the bus is shown for STS-1 number 1. STS-1 number 2 will occur one clock cycle later. There is always a one byte delay between the output ADATA and AC1J1/ASPE inputs.

| Parameter                                             | Symbol             | Min  | Тур   | Max  | Unit |

|-------------------------------------------------------|--------------------|------|-------|------|------|

| ACLK clock period                                     | t <sub>CYC</sub>   |      | 51.44 |      | ns   |

| ACLK duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                    | 40   | 50    | 60   | %    |

| AC1J1 set-up time to ACLK $\downarrow$                | t <sub>SU(1)</sub> | 7.0  |       |      | ns   |

| AC1J1 hold time after ACLK↓                           | t <sub>H(1)</sub>  | 3.0  |       |      | ns   |

| ASPE set-up time to ACLK $\downarrow$                 | t <sub>SU(2)</sub> | 10.0 |       |      | ns   |

| ASPE hold time after ACLK $\downarrow$                | t <sub>H(2)</sub>  | 5.0  |       |      | ns   |

| Data output delay from ACLK $\uparrow$                | t <sub>D(1)</sub>  |      |       | 30.0 | ns   |

| Add low output delay from ACLK1                       | t <sub>D(2)</sub>  |      |       | 15.0 | ns   |

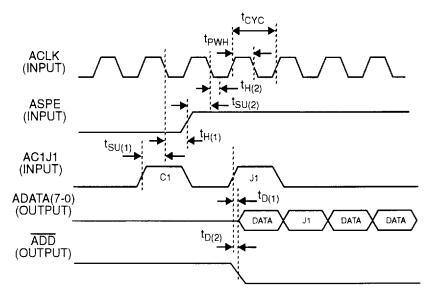

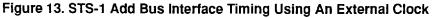

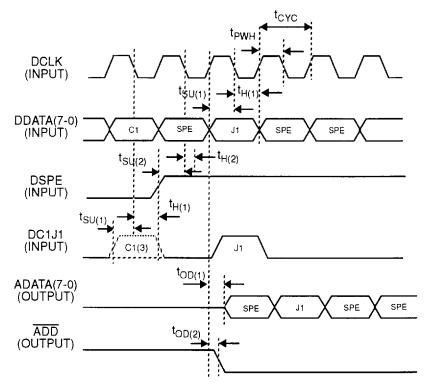

#### Figure 9. STS-1 Add Bus Derived Interface Timing

Note: The relationship between J1 and the SPE signal is shown for illustration purposes only. There is always a one byte delay between the output ADATA and AC1J1/ASPE inputs.

| Parameter                                             | Symbol             | Min  | Тур    | Мах     | Unit |

|-------------------------------------------------------|--------------------|------|--------|---------|------|

| ACLK clock period                                     | t <sub>CYC</sub>   |      | 154.32 |         | ns   |

| ACLK duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                    | 40   | 50     | 60      | %    |

| AC1J1 set-up time to ACLK $\downarrow$                | t <sub>SU(1)</sub> | 7.0  |        |         | ns   |

| AC1J1 hold time after ACLK $\downarrow$               | t <sub>H(1)</sub>  | 3.0  |        | <u></u> | ns   |

| ASPE set-up time to ACLK $\downarrow$                 | t <sub>SU(2)</sub> | 10.0 |        |         | ns   |

| ASPE hold time after ACLK $\downarrow$                | t <sub>H(2)</sub>  | 5.0  |        |         | ns   |

| Data output delay from ACLK1                          | t <sub>D(1)</sub>  |      |        | 30.0    | ns   |

| Add low output delay from ACLK <sup>↑</sup>           | t <sub>D(2)</sub>  |      |        | 15.0    | ns   |

TRA

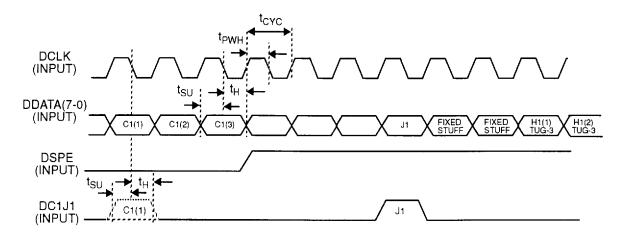

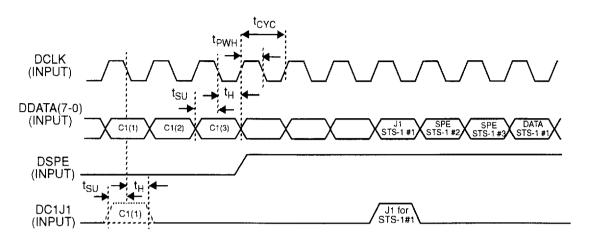

### Figure 10. STM-1 Drop Bus Interface Timing

Note: The relationship between J1 and the SPE signals is shown for illustration purposes only, and will be a function of the pointer offset. For the STM-1 format, there will be one J1 pulse which indicates the start of the VC-4 that carries the three TUG-3s. The C1 pulse is shown dotted because the C1 pulse may be provided on the DC1 signal lead. If the DC1 signal lead is not used, it must be grounded.

| Parameter                                             | Symbol          | Min | Тур   | Max | Unit |

|-------------------------------------------------------|-----------------|-----|-------|-----|------|

| DCLK clock period                                     | tcyc            |     | 51.44 |     | ns   |

| DCLK duty cycle (t <sub>PWH</sub> /t <sub>CYC</sub> ) |                 | 40  | 50    | 60  | %    |

| Data/DC1J1 set-up time to DCLK↓                       | t <sub>SU</sub> | 7.0 |       |     | ns   |

| Data/DC1J1 hold time after DCLK $\downarrow$          | t <sub>H</sub>  | 3.0 |       |     | ns   |

L3M

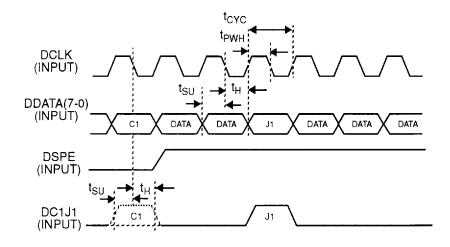

Figure 11. STS-3 Drop Bus Interface Timing